Применение микросхемы U664BS высокочастотного цифрового делителя частоты способствовало упрощению конструкции устройства, которое автор использовал для расширения диапазона измерений относительно низкочастотного частотомера. Делитель можно конструктивно оформить как переходник между входным гнездом и кабелем к источнику сигнала либо встроить в имеющийся любительский частотомер с дополнительным высокочастотным входом.

В радиолюбительской литературе уже были опубликованы схемы делителей частоты (например [1, 2]), предназначенных для использования с низкочастотным частотомером. Делитель, описанный в [1], при относительной простоте позволяет увеличить верхнюю частотную границу прибора всего лишь в 10 раз. Делитель частоты из [2] имеет коэффициент деления 100, но, на мой взгляд, его устройство неоправданно усложнено как по номенклатуре примененных деталей, так и по технической реализации.

Между тем, используя современную элементную базу, можно значительно упростить схему делителя частоты без необходимости программирования в случае применения микроконтроллера [3]. Описываемый делитель имеет коэффициент деления, равный 100, и диапазон устойчивой работы 25 МГц... 1 ГГц {верхняя граница соответствует паспортному значению частоты входного делители). Чувствительность делителя составляет 20 мВ при входном сопротивлении 50 Ом.

Схема делителя приведена на рис. 1. Микросхема U664BS (TELEFUNKEN) представляет собой монолитный цифровой делитель частоты в отношении 1:64. Эта микросхема выполнена по технологии ЭСЛ (змиттерно-связанной логики), ее транзисторы имеют граничную частоту frp = 4,5 ГГц. Диоды с барьером Шотки (VD1, VD2) служат для защиты входа микросхемы DD1 от сигналов большой амплитуды.

Как известно, логические уровни ЭСЛ в стандартном включении находятся в области напряжения отрицательной полярности и поэтому они непосредственно не совместимы с логическими уровнями микросхем ТТЛ и КМОП. Для преобразования уровней ЭСЛ в уровни ТТЛ при питании микросхемы ЭСЛ от напряжения плюсовой полярности служит согласующий каскад на транзисторе VT1.

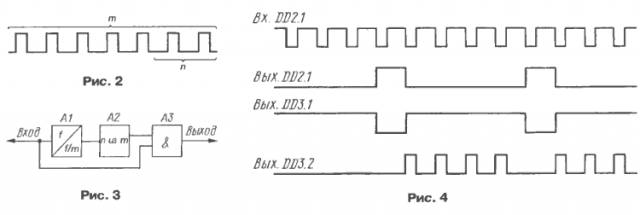

Входной сигнал с частотой, поделенной на 64, поступает на следующие два делителя, выполненных на микросхемах DD2 (К555ИЕ20) и DD3 (К155ТЛЗ). Микросхема К555ИЕ20 содержит два четырехразрядных двоично-десятичных счетчика каждый из них имеет триггер со входом С1, выходом 1 и делитель частоты на 5 со входом С2 и выходами 2, 4, 8. В этом устройстве счетчики DD2 работают в режиме делителя частоты на пять со входом С2 и выходом 8. Кстати, исходя из моей практики, верхняя рабочая частота всего устройства определяется максимальной частотой для счетчика DD2.1 (К555ИЕ20), которая по входам С2 обычно не менее 20 МГц, т. е. фактически не менее 1,28 ГГц. Каждый из делителей на DD2.1, DD3.1, DD3.2 и DD2 2, DD3.3. DD3.4 имеет дробный коэффициент деления Кя= 1,25 (или 5/4).

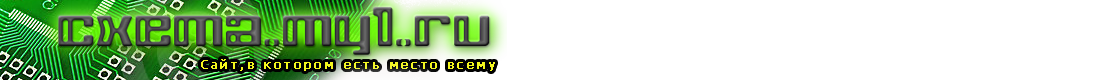

Суть использованного способа дробного деления частоты состоит в следующем. Пусть имеется последовательность импульсов, следующих с частотой F (рис. 2) Если из каждой пачки, образованной m импульсами, исключить n импульсов, то средняя частота следовании импульсов в новой последовательности

Fo=(m-n)/m*F

Коэффициент деления имеет вид отношения двух чисел КД = m/(m-n),: т. е. в общем случае представляет неправильную дробь.

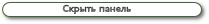

В общем виде структурная схема дробного делителя частоты показана на рис. 3. Его основу составляет делитель А1 на целое число т. Формирователь А2 создает импульс длительностью, равной n периодов входной последовательности импульсов.: Устройство совпадения A3 выделяет импульсы числом (m-п) из каждой последовательности в гп импульсов.

В нашем случае m = 5 и n = 1. Триггеры Шмитта логических элементов микросхемы D03 позволяют использовать схему совпадения для четкого выделения только четыре> импульсов из каждых пяти входных импульсов, поступающих на счетчики микросхемы DD2. На рис. 4 показаны временные диаграммы поясняющие работу каждого из двух каскадно включенных дробных делителей.

Таким образом, если на вход описываемою делителя частоты поступает сигнал частотой, например, F = 1000 МГц, то после первого делителя DD1 частота F2 = F1/64 = 15,625 МГц. После второго делителя (с DD2.1) частота станет равной F2 = F1/1,25 = 12,5 МГц и после третьего — F2/1,25 = 10 МГц

Все элементы делителя размещены на плате из фольгированного стеклотекстолита. Чертеж печатной платы представлен на рис. 5. Плату следует поместить в металлический экран. Вход и выход делителя соединяют с частотомером ВЧ кабелем

Если частотомер выполнен в виде законченной малогабаритной конструкции, делитель можно конструктивно оформить как переходник между входным гнездом и кабелем к источнику сигнала. Для этого плату нужно поместить в прямоугольный экран, в торцах которого смонтировать разъемы СР-50-75: с одной стороны — штыревую часть разъема, с другой — гнездовую.

Делитель частоты был испытан совместно с частотомером, описанным в [4], и показал отличные результаты.

Рис.5

ЛИТЕРАТУРА

- Бирюков С. А. Предварительный делитель. — Радио, 1980, № 10, с- 61.

- Жук В. Предварительный делитель частоты на диапазон 50 .1500 МГц. — Радио, 1992, № 10. с. 46, 47

- Нечаев И. Делитель частоты диапазона 0.1. .3.5 ГГц. — Радио. 2005. № 9, с. 24—26.

- Бирюков С. Цифровой частотомер — Радио, 1981, № 10, с. 44 47.